Documentos Técnicos

Especificações

Brand

NexperiaLogic Function

NAND

Product Type

Quad 2-input NAND Gate

Mount Type

Surface

Number of Elements

4

Number of Inputs per Gate

2

Schmitt Trigger Input

No

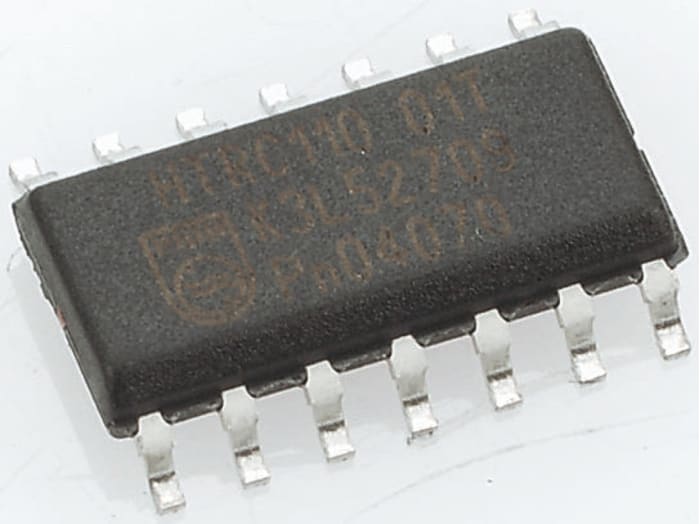

Package Type

SOIC

Pin Count

14

Logic Family

HC

Input Type

CMOS

Maximum Propagation Delay Time @ CL

29ns

Minimum Operating Temperature

-40°C

Maximum High Level Output Current

-5.2mA

Maximum Operating Temperature

125°C

Minimum Supply Voltage

2V

Height

1.45mm

Length

8.75mm

Standards/Approvals

JEDEC Standard No. 7A

Series

74HC03

Maximum Supply Voltage

6V

Maximum Low Level Output Current

5.2mA

Output Type

Open Drain

Automotive Standard

No

País de Origem

Thailand

Detalhes do produto

74HC Family Logic Gates, Nexperia

A range of NXP standard Logic Gates from the 74HC Family of CMOS Logic ICs. The 74HC Family use silicon gate CMOS technology to achieve operating speeds similar to the LSTTL family but with the low power consumption of standard CMOS integrated circuits.

74HC Family

Informações de estoque temporariamente indisponíveis.

R$ 105,45

R$ 1,85 Each (In a Tube of 57) (Sem VAT)

57

R$ 105,45

R$ 1,85 Each (In a Tube of 57) (Sem VAT)

Informações de estoque temporariamente indisponíveis.

57

Documentos Técnicos

Especificações

Brand

NexperiaLogic Function

NAND

Product Type

Quad 2-input NAND Gate

Mount Type

Surface

Number of Elements

4

Number of Inputs per Gate

2

Schmitt Trigger Input

No

Package Type

SOIC

Pin Count

14

Logic Family

HC

Input Type

CMOS

Maximum Propagation Delay Time @ CL

29ns

Minimum Operating Temperature

-40°C

Maximum High Level Output Current

-5.2mA

Maximum Operating Temperature

125°C

Minimum Supply Voltage

2V

Height

1.45mm

Length

8.75mm

Standards/Approvals

JEDEC Standard No. 7A

Series

74HC03

Maximum Supply Voltage

6V

Maximum Low Level Output Current

5.2mA

Output Type

Open Drain

Automotive Standard

No

País de Origem

Thailand

Detalhes do produto

74HC Family Logic Gates, Nexperia

A range of NXP standard Logic Gates from the 74HC Family of CMOS Logic ICs. The 74HC Family use silicon gate CMOS technology to achieve operating speeds similar to the LSTTL family but with the low power consumption of standard CMOS integrated circuits.